엔비디아 AI 칩의 폭발적인 성능 뒤에는 TSMC의 CoWoS(Chip on Wafer on Substrate) 패키징 기술이 핵심적인 역할을 합니다. 단순히 칩을 연결하는 것을 넘어, GPU와 HBM(고대역폭 메모리)을 초고속으로 통합하여 데이터 통신 병목 현상을 제거하는 게임 체인저죠. 실제로 엔비디아의 H100, B200과 같은 최신 AI 가속기가 고성능을 낼 수 있는 비결도 바로 이 CoWoS 기술 덕분입니다.

하지만 이 필수 기술이 AI 칩 공급망의 가장 큰 병목 현상으로 지목되며, 엔비디아 CEO 젠슨 황조차 TSMC 외에는 대안이 없다고 언급할 정도입니다. 과연 TSMC의 CoWoS 생산 능력은 급증하는 AI 칩 수요를 감당할 수 있을까요? 그리고 엔비디아의 압도적인 CoWoS 물량 선점은 AI 산업 전반에 어떤 영향을 미칠까요? 이 글에서는 TSMC CoWoS 기술의 중요성부터 2026년까지의 생산 능력 전망, 그리고 엔비디아 AI 칩 공급망의 숨겨진 리스크까지, 당신이 궁금해할 모든 것을 심층적으로 분석해 드립니다.

Nvidia AI 칩, CoWoS가 왜 핵심인가?

엔비디아 AI 칩의 뛰어난 성능 뒤에는 TSMC의 CoWoS(Chip on Wafer on Substrate) 패키징 기술이 핵심적인 역할을 합니다. 이 기술은 여러 개의 칩을 하나의 기판 위에 효율적으로 통합하여, AI 칩 성능 향상에 필수적인 요소로 평가받고 있어요. 특히 GPU와 HBM(고대역폭 메모리)을 초고속으로 연결해 데이터 통신 효율을 극대화하고 전력 소모를 줄이는 것이 특징입니다.

CoWoS가 AI 칩 성능을 높이는 원리

엔비디아의 최신 AI 가속기인 H100이나 블랙웰 같은 제품들이 고성능을 낼 수 있는 비결도 바로 CoWoS 기술 덕분입니다. 이 기술은 GPU와 HBM 간의 데이터 통신 병목 현상을 해소하여 전체적인 칩의 효율을 높여줍니다.

- 초고속 데이터 통신: GPU와 HBM 간 물리적 거리를 최소화하여 데이터 전송 지연을 줄입니다.

- 전력 효율성 증대: 짧아진 데이터 경로 덕분에 전력 소모를 줄여 칩의 효율을 높입니다.

- 소형화 및 집적도 향상: 여러 칩을 한 번에 패키징하여 전체 칩 크기를 줄이고 더 많은 기능을 집적할 수 있습니다.

이처럼 CoWoS 기술은 AI 칩의 성능을 좌우하는 핵심 요소이며, TSMC의 CoWoS 기술은 엔비디아 AI 칩의 성능을 극대화하는 데 결정적인 역할을 하고 있습니다.

CoWoS, AI 시대의 새로운 병목 현상

TSMC의 CoWoS 패키징 기술은 엔비디아 AI 칩의 핵심이지만, 이 기술에 대한 높은 의존성은 AI 산업 전체의 발전을 저해하는 심각한 병목 현상으로 작용하고 있습니다. CoWoS 생산 능력 부족은 AI 반도체 수요가 폭발적으로 증가하면서 더욱 두드러지고 있으며, 이는 AI 산업의 혁신 속도를 좌우하는 핵심 요소로 부상했습니다.

CoWoS가 AI 시대의 병목 현상인 이유

CoWoS 기술은 여러 칩을 하나의 기판에 통합하여 초고속 데이터 전송과 전력 효율성을 극대화하는 첨단 패키징 방식입니다. 이 기술은 AI 칩 성능을 결정짓는 핵심 요소이지만, 생산 공정이 매우 복잡하고 고도의 기술력을 요구합니다. 현재 TSMC가 이 분야에서 독보적인 기술력과 생산 능력을 보유하고 있어, 엔비디아를 비롯한 주요 AI 칩 개발사들이 TSMC에 크게 의존할 수밖에 없는 상황입니다.

엔비디아는 AI GPU 수요를 충족시키기 위해 TSMC의 CoWoS 생산 능력 대부분을 선점하고 있으며, 이는 다른 고객사들의 공급 제약으로 이어져 AI 반도체 시장 전반의 성장을 늦추는 요인이 됩니다. TSMC의 CoWoS 생산 능력은 2023년 12.3만 웨이퍼에서 2025년 60.9만 웨이퍼로 크게 증가할 것으로 예상되지만, AI 반도체 수요 급증으로 인해 여전히 공급 병목 현상이 지속될 수 있다는 분석이 있습니다.

특정 기술에 대한 높은 의존성은 AI 산업 전체의 발전 속도를 좌우하는 핵심 병목 현상으로, AI 칩 공급망의 복잡성과 취약성을 명확히 보여줍니다.

TSMC, CoWoS 생산 능력 확대 현황은?

TSMC는 AI 반도체 수요 폭증에 발맞춰 CoWoS 생산 능력을 공격적으로 확대하고 있습니다. 2023년 연간 12.3만 웨이퍼였던 생산 용량은 2025년에는 60.9만 웨이퍼로 크게 늘어날 것으로 예상되며, 이는 AI 칩 공급 병목 현상을 해소하는 데 중요한 역할을 할 것으로 기대됩니다.

TSMC의 CoWoS 생산 능력 확대 현황

TSMC는 AI 반도체 시장의 요구에 부응하기 위해 CoWoS 생산 능력을 꾸준히 늘리고 있습니다. 구체적인 목표는 다음과 같습니다.

- 2023년: 연간 12.3만 웨이퍼 생산

- 2024년: 연간 30.9만 웨이퍼 생산 목표

- 2025년: 연간 60.9만 웨이퍼 생산 목표

이러한 생산 능력 확대는 엔비디아와 같은 주요 고객사의 AI 칩 수요를 충족시키기 위한 TSMC의 적극적인 노력으로 볼 수 있습니다. 하지만 생산 능력 확장에도 불구하고, 지정학적 위험, 기술 난이도, 그리고 폭발적인 수요 증가가 복합적으로 작용하여 AI 칩 공급망의 불안정성은 지속될 수 있다는 분석이 있습니다.

실용적인 조언: AI 칩 공급망의 불확실성을 고려할 때, 장기적인 관점에서 공급처 다변화나 기술 개발 로드맵을 유연하게 가져가는 것이 중요합니다.

AI 칩 공급망, 불안정성은 왜 지속될까?

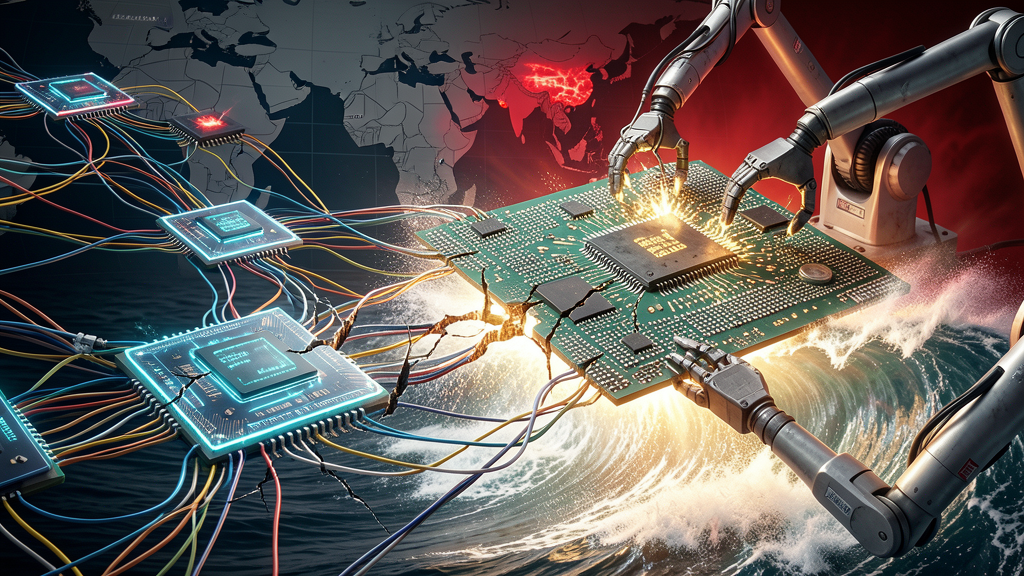

TSMC가 CoWoS 생산 능력을 확대하고 있음에도 불구하고, AI 칩 공급망의 불안정성은 쉽게 해소되지 않을 전망입니다. 이는 단순히 생산량 증대만으로는 해결하기 어려운 구조적인 문제들이 복합적으로 작용하기 때문입니다.

AI 칩 공급망 불안정성의 주요 원인

AI 칩 공급망의 불안정성이 지속되는 주요 원인은 크게 세 가지로 볼 수 있습니다. 첫째, 지정학적 위험은 대만 해협의 긴장 고조나 미국의 대중국 반도체 수출 규제 강화와 같이 언제든 공급망에 큰 변동성을 초래할 수 있습니다. 둘째, 기술 난이도는 CoWoS와 같은 첨단 패키징 기술의 생산을 제한하는 요인입니다. 이 기술은 매우 복잡하고 정교한 공정을 요구하기 때문에, 생산 라인을 빠르게 확장하거나 대체할 수 있는 기업이 극히 드뭅니다. 셋째, 수요 폭증은 AI 기술 발전과 함께 AI 칩에 대한 수요가 기하급수적으로 증가하고 있어, 공급이 아무리 늘어도 이를 따라잡기 어렵게 만듭니다.

- 지정학적 위험: 대만 집중 생산에 따른 지정학적 불확실성

- 기술 난이도: CoWoS와 같은 첨단 패키징 공정의 높은 기술 장벽

- 수요 폭증: AI 기술 발전과 함께 빠르게 증가하는 칩 수요

이러한 구조적 원인들 때문에 TSMC가 2026년까지 월 12만 5천~13만 장의 웨이퍼 생산 능력을 목표로 CoWoS 생산량을 늘려도, AI 칩 공급망의 불안정성은 완전히 해소되기 어려울 것으로 보입니다. 특히 엔비디아가 2026년에도 TSMC CoWoS 생산 능력의 절반 이상을 선점할 것으로 예상되는 점은 다른 기업들의 공급 제약을 심화시킬 수 있습니다.

CoWoS 기술 진화와 AI 산업의 미래 전망

CoWoS 기술은 AI 칩 성능 향상의 핵심 동력으로 계속 진화하며, AI 산업의 미래를 좌우할 중요한 요소로 자리매김하고 있습니다. 엔비디아가 최신 블랙웰 아키텍처 GPU에 CoWoS-S 대신 CoWoS-L 기술을 주로 사용할 것이라고 밝힌 것처럼, CoWoS는 다양한 유형으로 발전하고 있습니다. 이러한 기술 진화는 AI 칩의 성능을 더욱 끌어올리고 전력 효율성을 극대화하는 데 기여할 것입니다.

CoWoS 기술 진화와 AI 산업의 미래

TSMC는 2025년 CoWoS 플랫폼에 직접 실리콘 액체 냉각 기술을 시연하며 2.6kW 이상의 TDP에서도 안정적인 열 관리가 가능함을 입증했습니다. 이는 고성능 AI 칩의 안정적인 구동에 필수적인 요소로, 향후 AI 데이터센터의 발전 방향을 제시합니다. CoWoS 기술은 단순히 칩을 쌓는 것을 넘어, 고성능화, 전력 효율성 향상, 그리고 집적도 향상이라는 세 가지 방향으로 진화하고 있습니다.

CoWoS 외에도 인텔의 EMIB(Embedded Multi-die Interconnect Bridge)와 같은 경쟁 기술들이 존재하지만, TSMC의 CoWoS 기술은 AI 칩 패키징 시장에서 중요한 위치를 차지하고 있습니다. TSMC는 2026년 말까지 월 12만 5천~13만 웨이퍼 수준으로 CoWoS 생산 능력을 확대할 계획이며, 엔비디아는 2026년 TSMC CoWoS 물량의 절반 이상인 연간 약 80만~85만 장의 웨이퍼를 선점할 것으로 예상됩니다. CoWoS 기술의 발전과 공급 안정성은 AI 산업의 지속적인 성장에 결정적인 영향을 미칠 것입니다.

CTA

TSMC CoWoS 기술이 AI 칩 성능과 공급망에 미치는 영향에 대한 더 깊은 통찰력을 얻고 싶다면, 관련 심층 분석 보고서를 확인해 보세요.

FAQ

Nvidia AI 칩, CoWoS가 왜 핵심인가?

엔비디아 AI 칩의 뛰어난 성능 뒤에는 TSMC의 CoWoS(Chip on Wafer on Substrate) 패키징 기술이 핵심적인 역할을 합니다. 이 기술은 여러 개의 칩을 하나의 기판 위에 효율적으로 통합하여, AI 칩 성능 향상에 필수적인 요소로 평가받고 있어요.

CoWoS, AI 시대의 새로운 병목 현상은 무엇인가요?

TSMC의 CoWoS 패키징 기술은 엔비디아 AI 칩의 핵심이지만, 이 기술에 대한 높은 의존성은 AI 산업 전체의 발전을 저해하는 심각한 병목 현상으로 작용하고 있습니다. CoWoS 생산 능력 부족은 AI 반도체 수요가 폭발적으로 증가하면서 더욱 두드러지고 있으며, 이는 AI 산업의 혁신 속도를 좌우하는 핵심 요소로 부상했습니다.

TSMC, CoWoS 생산 능력 확대 현황은?

TSMC는 AI 반도체 수요 폭증에 발맞춰 CoWoS 생산 능력을 공격적으로 확대하고 있습니다. 2023년 연간 12.3만 웨이퍼였던 생산 용량은 2025년에는 60.9만 웨이퍼로 크게 늘어날 것으로 예상되며, 이는 AI 칩 공급 병목 현상을 해소하는 데 중요한 역할을 할 것으로 기대됩니다.

AI 칩 공급망, 불안정성은 왜 지속될까?

TSMC가 CoWoS 생산 능력을 확대하고 있음에도 불구하고, AI 칩 공급망의 불안정성은 쉽게 해소되지 않을 전망입니다. 이는 단순히 생산량 증대만으로는 해결하기 어려운 구조적인 문제들이 복합적으로 작용하기 때문입니다.

CoWoS 기술 진화와 AI 산업의 미래 전망은 무엇인가요?

CoWoS 기술은 AI 칩 성능 향상의 핵심 동력으로 계속 진화하며, AI 산업의 미래를 좌우할 중요한 요소로 자리매김하고 있습니다. 엔비디아가 최신 블랙웰 아키텍처 GPU에 CoWoS-S 대신 CoWoS-L 기술을 주로 사용할 것이라고 밝힌 것처럼, CoWoS는 다양한 유형으로 발전하고 있습니다.